Rambus a récemment présenté de nouvelles normes de mémoire DDR5, promettant des performances révolutionnaires atteignant des vitesses de 12 800 MT/s.

Rambus Élever les Vitesses DDR5 à 12 800 MT/s avec les Nouveaux MRDIMMs

Dans un communiqué de presse, Rambus, un fournisseur de puces et de propriété intellectuelle en silicium de premier plan, a dévoilé des chipsets d’interface mémoire de classe mondiale pour les RDIMMs DDR5 Gen5 et les nouveaux modules mémoire à rang multiplexé dual inline (MRDIMMs). Ces produits de pointe sont conçus pour optimiser les performances des DDR5, offrant une bande passante et une capacité mémoire inégalées pour les centres de données intensifs en calcul et les charges de travail d’IA.

Les nouveaux chips Rambus incluent le Gen5 Registering Clock Driver (RCD), qui permet aux RDIMMs de fonctionner à 8000 MT/s. Les Multiplexed Registering Clock Driver (MRCD) et Multiplexed Data Buffer (MDB) font passer les futurs MRDIMMs à des vitesses atteignant 12 800 MT/s, doublant ainsi la bande passante au-delà de la vitesse native des dispositifs DRAM.

Le Power Management IC (PMIC5030) de deuxième génération est également prévu, fonctionnant à la fois avec les RDIMMs DDR5 8000 et les MRDIMMs 12800, tout en offrant un courant ultra-élevé à faible tension. Cela soutient des vitesses plus élevées et un plus grand nombre de puces DRAM et logiques par module.

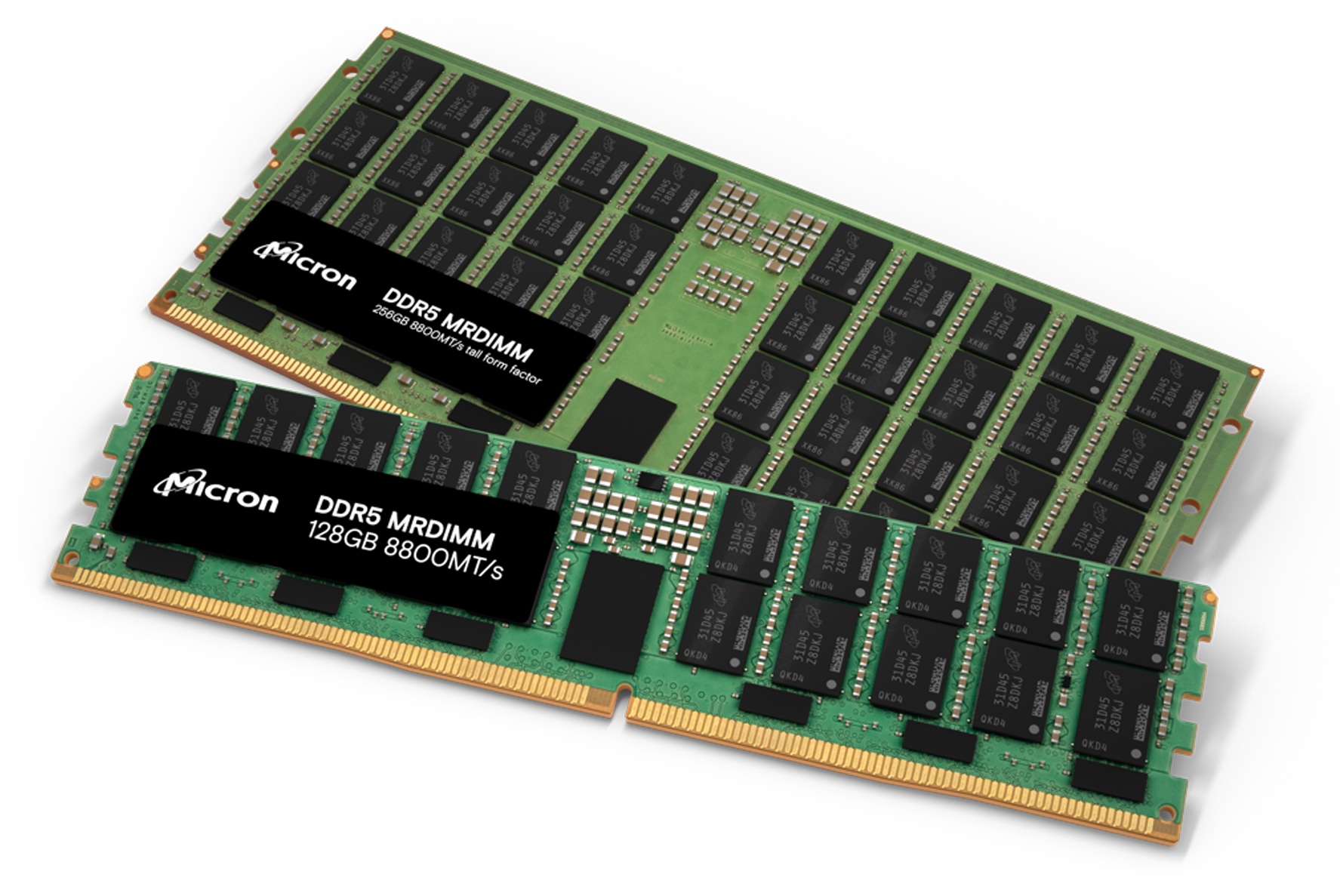

Les RDIMMs DDR5 8000 et les MRDIMMs 12800 sont conçus pour permettre une configuration de serveur flexible et évolutive. Leur architecture commune assure la compatibilité à travers les plates-formes serveur. Le chipset RDIMM 8000 comprend le Gen5 RCD, le PMIC5030, un Hub de Détection de Présence Sérielle (SPD), ainsi qu’un capteur de température (TS). Le chipset MRDIMM 12800 inclut le MRCD et le MDB, en plus des mêmes PMIC5030, SPD Hub et TS utilisés dans le RDIMM 8000.

Le design novateur du DDR5 MRDIMM 12800 permet une bande passante accrue grâce à une architecture multiplexée de deux rangs de DRAM. Cette méthode intercale les deux flux de données pour que le bus mémoire puisse fonctionner à deux fois le taux de données des dispositifs DRAM natifs, tout en utilisant les mêmes connexions physiques que les RDIMMs DDR5.

Pour réaliser cela, un MRCD doit être capable d’adresser les deux rangs de DRAMs à des cycles d’fréquence alternés, tandis que les MDBs dirigent le flux de données entre les dispositifs DRAM appropriés. Chaque DDR5 MRDIMM 12800 exige un MRCD et dix MDBs pour multiplexage du canal mémoire. Le MRCD et les MDBs peuvent également être intégrés dans un design (form factor) Tall MRDIMM, lequel permet de doubler la capacité d’un RDIMM à double rang de manière rentable.

Les composants Gen5 RCD, MRCD, MDB et PMIC5030 s’inscrivent dans le large éventail de solutions d’interface mémoire et de gestion de l’alimentation proposées par Rambus, incluant les RCD Gen1 à Gen4, le Client Clock Driver (CKD), le PMIC serveur, ainsi que les composants SPD Hub et TS.