PCI-SIG a publié cette semaine la version 0.5 de la caractéristique PCI-Express 7.0 à ses membres. Il s’agit du deuxième brouillon de la caractéristique et de l’appel final aux membres de PCI-SIG pour soumettre leurs nouvelles fonctionnalités à la norme. La dernière mise à jour sur le développement de la caractéristique intervient quelques mois avant un an après que PCI-SIG ait publié la caractéristique initiale Draft 0.3, avec la dernière mise à jour pour réaffirmer que le développement de la nouvelle norme est en bonne voie pour une publication finale en 2025.

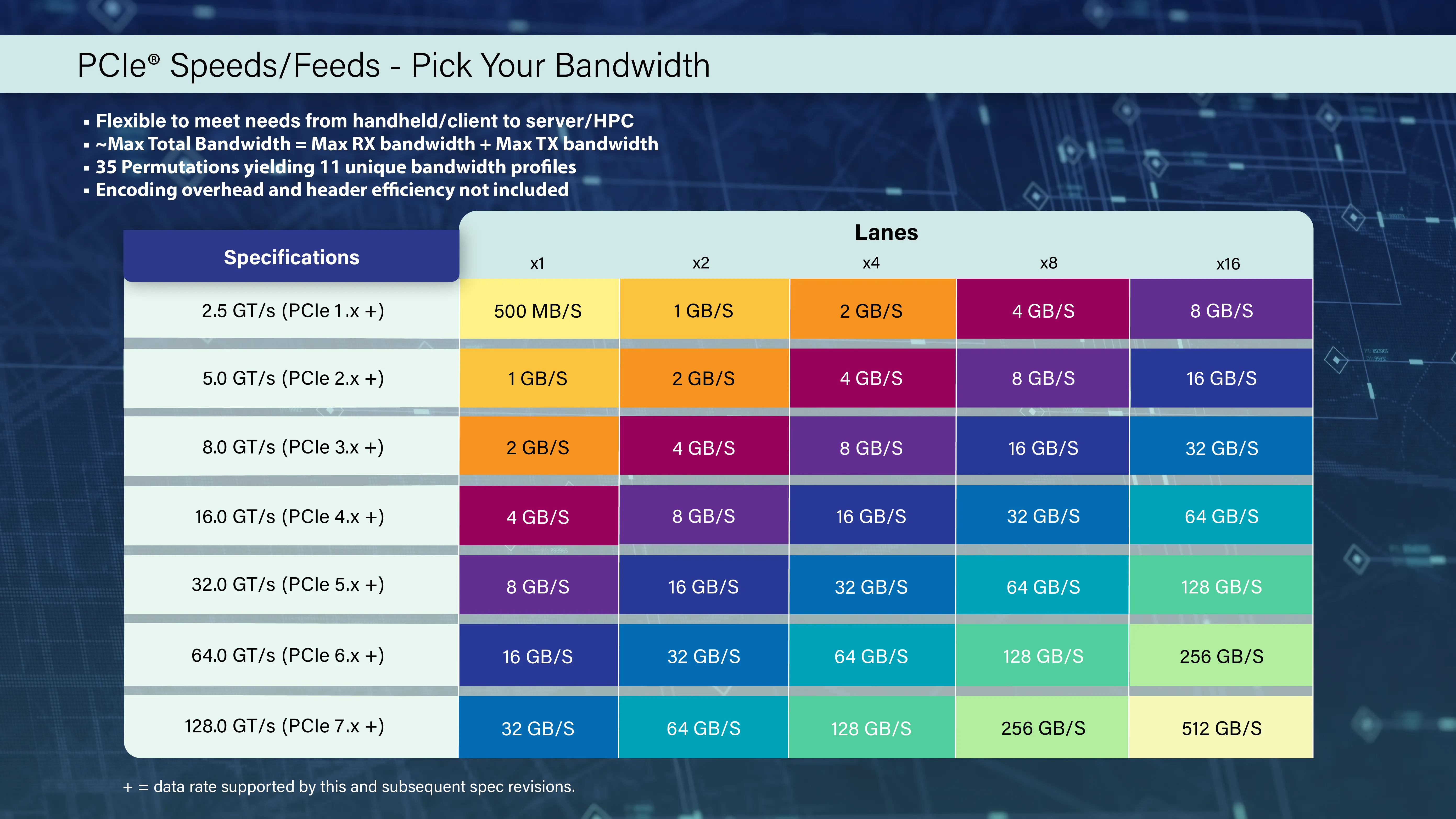

PCIe 7.0 est la prochaine technologie d’interconnexion de nouvelle génération pour les ordinateurs qui devrait augmenter les vitesses de transfert de données à 128 GT/s par broche, soit le double des 64 GT/s de PCIe 6.0 et le quadruple des 32 GT/s de PCIe 5.0. Cela permettrait à une connexion de 16 voies (x16) de prendre en charge 256 Go/s de bande passante dans chaque direction simultanément, en excluant les frais généraux d’encodage. De telles vitesses seront utiles pour les futurs centres de données ainsi que pour l’intelligence artificielle et les applications de calcul haute performance qui auront besoin de taux de transfert de données encore plus rapides, y compris les taux de transfert de données réseau.

Pour atteindre ses impressionnants taux de transfert de données, PCIe 7.0 double la fréquence du bus au niveau physique par rapport à PCIe 5.0 et 6.0. Sinon, la norme conserve la modulation d’amplitude d’impulsion avec signalisation à quatre niveaux (PAM4), le codage en mode FLIT 1b/1b et les technologies de correction d’erreur vers l’avant (FEC) déjà utilisées pour PCIe 6.0. Par ailleurs, PCI-SIG indique que la caractéristique PCIe 7.0 se concentre également sur des paramètres et une portée de canal améliorés ainsi que sur une efficacité énergétique accrue.

Dans l’ensemble, les ingénieurs derrière la norme ont du pain sur la planche, étant donné que PCIe 7.0 nécessite de doubler la fréquence du bus au niveau physique, un développement majeur que PCIe 6.0 a contourne en utilisant la signalisation PAM4. Rien ne vient gratuitement en ce qui concerne l’amélioration de la signalisation des données, et avec PCIe 7.0, le PCI-SIG est sans doute de retour en mode difficile en ayant besoin d’améliorer une fois de plus la couche physique – cette fois-ci pour lui permettre de fonctionner à environ 30 GHz. Toutefois, il reste à voir dans quelle mesure cette tâche difficile sera réalisée grâce à une signalisation intelligente (et des retimers) et dans quelle mesure elle sera accomplie grâce à des améliorations matérielles pures, telles que des cartes de circuits imprimés (PCB) plus épaisses et des matériaux à faible perte.

La prochaine étape majeure pour PCIe 7.0 est la finalisation de la version 0.7 de la caractéristique, qui est considérée comme le brouillon complet, où tous les aspects doivent être entièrement définis et les caractéristiques électriques doivent être validées par le biais de puces de test. Après la publication de cette itération de la caractéristique, aucune nouvelle fonctionnalité ne pourra être ajoutée. PCIe 6.0 est passé par 4 brouillons majeurs – 0.3, 0.5, 0.7 et 0.9 – avant d’être finalement finalisé, il est donc probable que PCIe 7.0 suive le même parcours.

Une fois finalisée en 2025, il faudra quelques années avant que le premier hardware PCIe 7.0 ne soit disponible sur les sites marchands. Bien que les travaux de développement sur les IP de contrôleur et le hardware initial soient déjà en cours, ce processus s’étend bien au-delà de la publication de la caractéristique finale de PCIe.