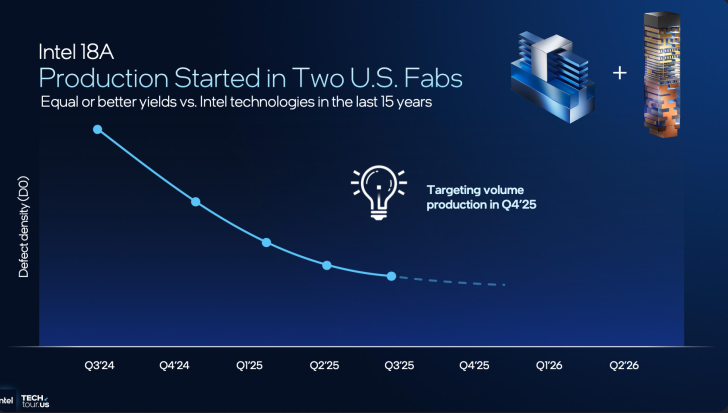

Intel a dévoilé des avancées concernant la puce 18A lors du Tech Tour, affirmant que la densité de défauts atteint un niveau historiquement bas.

La Densité de Défauts de l’18A d’Intel et Ses Implications pour la Production

Le nœud 18A s’annonce comme l’une des sorties les plus déterminantes pour Intel Foundry. À l’heure où les capacités de fabrication des puces d’Intel sont observées de près par des entités politiques et commerciales, l’équipe a l’obligation de garantir une solution efficace. Les discussions lors de la keynote de l’ITT indiquent que la densité de défauts de la 18A est actuellement à son minimum, avec une production de masse prévue pour le quatrième trimestre.

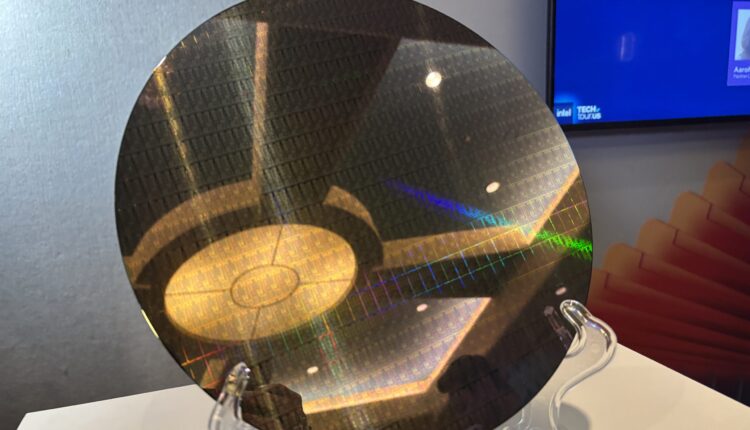

Cet aspect est crucial pour 18A, car il indique une compétitivité dans la production de masse. La densité de défauts désigne le nombre de défauts par unité de surface sur un wafer, ce qui peut nuire au bon fonctionnement des transistors. Une densité élevée irait à l’encontre des nombreux grands ensembles de puces envisagés avec 18A, qui devrait répondre aux besoins du marché.

La densité de défauts, particulièrement basse, est essentielle pour anticiper les taux de rendement de production. Historiquement, ceux-ci ont fluctué, allant jusqu’à des chiffres alarmants de 10%. Avec l’intensification de la fabrication de 18A, des taux de défauts réduits permettent à Intel de concevoir des superficies de puces plus larges, touchant ainsi des segments tels que le calcul haute performance.

Bien que la densité de défauts soit un indicateur clé, d’autres éléments comme les erreurs de masquage et les défaillances paramétriques doivent également être pris en compte. La réduction significative de la densité de défauts ouvre la voie à un package compétitif qui pourrait rivaliser avec les technologies TSMC N2 et Samsung SF2.

Suivez OMGPU sur Google ou ajoutez-nous comme source préférée pour suivre les actualités et avis dans vos flux.