Lors d’un événement majeur depuis sa séparation de Western Digital, SanDisk a présenté une innovation audacieuse visant à conquérir le marché florissant de l’IA. Son architecture de mémoire, appelée high-bandwidth flash, promet de révolutionner le stockage avec des capacités inégalées tout en répondant aux exigences croissantes des applications d’IA.

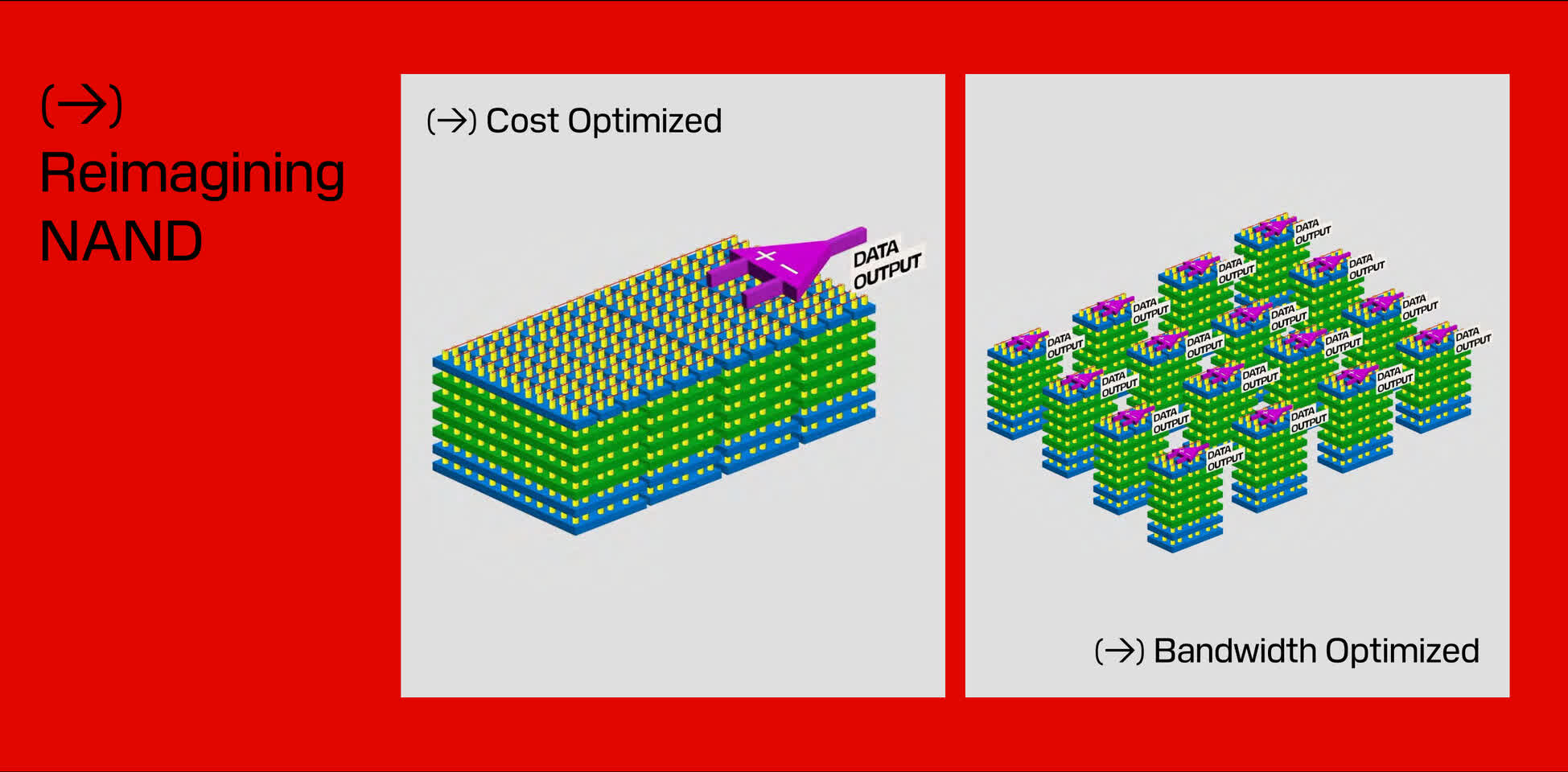

Que vient-il de se passer ? Lors de son premier grand événement pour les investisseurs depuis sa séparation de Western Digital, SanDisk a dévoilé quelque chose sur lequel il travaille pour s’implanter sur le chaud marché de l’IA. L’entreprise propose une nouvelle architecture de mémoire appelée high-bandwidth flash qui fusionne la capacité de stockage massive de la 3D NAND avec la bande passante offerte par la HBM.

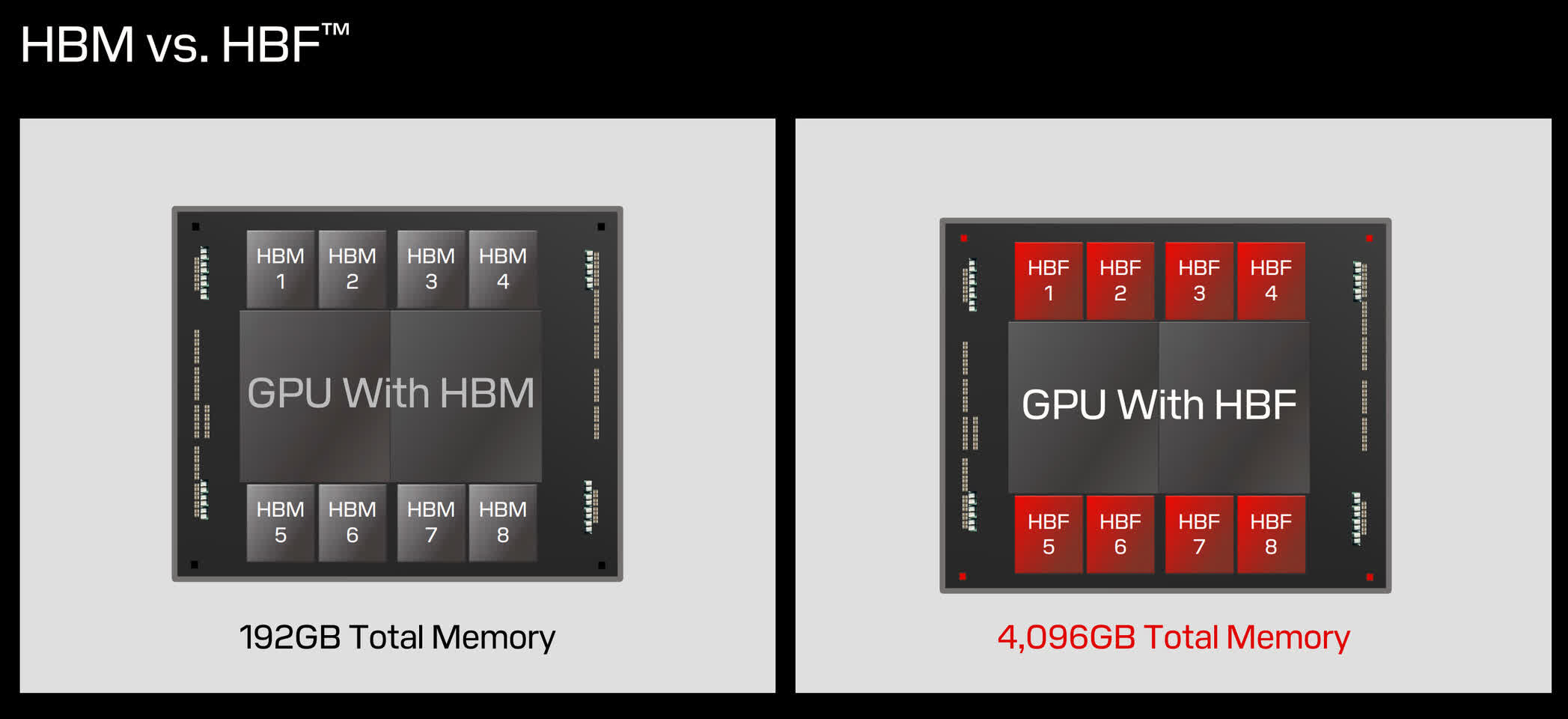

Cette création hybride empile un impressionnant 16 couches des dernières puces 3D NAND de SanDisk en utilisant de minuscules pipelines de données appelés vias à travers le silicium. Il existe également une couche logique spéciale qui peut transférer les données vers et depuis les sous-matrices NAND de manière parallèle. Cela permet à la HBF d’atteindre 8 à 16 fois plus de capacité par empilement que les implémentations HBM actuelles.

Dans un des exemples de SanDisk, un système équipé de huit empilements HBF pourrait offrir une capacité colossal de 4 téraoctets pour stocker d’encombrants modèles d’IA comme GPT-4 directement sur le hardware GPU.

L’innovation clé semble être que l’architecture de la HBF rompt avec les conceptions traditionnelles de la NAND en divisant chaque puce en de nombreuses sous-matrices minuscules pouvant être accessibles aléatoirement en parallèle, plutôt que traitées comme des plans et des pages basés sur des blocs plus grands. Cela permet une bande passante élevée tout en maintenant les avantages de coût et de capacité de la NAND.

Bien sûr, le talon d’Achille de la NAND a toujours été la latence plus élevée par rapport aux technologies DRAM comme la HBM. Comme l’a souligné Tom’s Hardware, la HBF ne fait pas exception et ne rivalise évidemment pas avec la rapidité fulgurante de la DRAM. La nouvelle architecture vise des charges de travail d’inférence d’IA intensivement en lecture qui nécessitent une haute bande passante et capacité mais peuvent tolérer une latence plus élevée. Des tâches comme le gaming sont exclues.

Il reste encore certains obstacles à surmonter pour cette technologie. SanDisk a été dédié sur la façon dont elle contournera les limites d’endurance d’écriture de la NAND, ainsi que sur l’adressage basé sur des blocs qui pourrait entraver l’accès aléatoire. Nous ne savons également pas quels types de chiffres de bande passante la HBF peut atteindre.

Malgré les questions restantes, il semble que SanDisk voit un grand potentiel. L’entreprise souhaite que la HBF devienne une norme ouverte pour compléter la HBM dans le hardware tel que les GPU. Pour y parvenir, elle s’associe déjà avec des partenaires constructeurs et prévoit trois générations complètes de développement de HBF, soulignant un investissement sérieux à long terme.

Finalement, SanDisk envisage même que cette technologie se répande des systèmes d’IA haut de gamme vers des appareils grand public comme les smartphones.