Mardi, JEDEC a publié les caractéristiques officielles du DRAM GDDR7, la dernière itération de la norme de mémoire de longue date pour les cartes graphiques et autres appareils équipés par GPU. La nouvelle génération de GDDR apporte une combinaison de capacité de mémoire et de gains de bande passante, ce dernier étant principalement entraîné par le passage à une signalisation PAM3 sur le bus mémoire. La dernière norme de RAM graphique augmente également le nombre de canaux par puce DRAM, ajoute de nouveaux motifs d’entraînement d’interface et intègre un ECC intégré pour maintenir la fiabilité effective de la mémoire.

« JESD239 GDDR7 représente une avancée substantielle dans la conception des mémoires haute vitesse », a déclaré Mian Quddus, président du conseil d’administration de JEDEC. « Avec le passage à une signalisation PAM3, l’industrie de la mémoire dispose d’une nouvelle voie pour étendre les performances des dispositifs GDDR et stimuler l’évolution continue des graphiques et de diverses applications hautes performances ».

GDDR7 est en cours de développement depuis quelques années maintenant, les membres de JEDEC ayant rendu les premières divulgations autour de la technologie mémoire il y a environ un an, lorsque Cadence a révélé l’utilisation du codage PAM3 dans leurs outils de validation. Depuis lors, nous avons entendu plusieurs constructeurs de mémoire dire que nous devrions nous attendre au lancement de la version finale de la mémoire en 2024, l’annonce de JEDEC intervenant essentiellement dans les délais prévus.

Comme cela a été précédemment dévoilé, le plus grand changement technique avec le GDDR7 vient du passage d’un codage NRZ (non retour à zéro) à deux bits sur le bus mémoire à un codage PAM3 à modulation d’amplitude d’impulsion à trois bits. Ce changement permet au GDDR7 de transmettre 3 bits sur deux cycles, soit 50% de données en plus que le GDDR6 fonctionnant à une fréquence identique. En conséquence, le GDDR7 peut prendre en charge des taux de transfert de données globaux plus élevés, composant essentiel pour que chaque génération de GDDR soit successivement plus rapide que son prédécesseur.

| Générations de GDDR | |||||

| GDDR7 | GDDR6X (Non-JEDEC) |

GDDR6 | |||

| B/W Par Broche | 32 Gbps (Gen 1) 48 Gbps (Max Spécifié) |

24 Gbps (Livraison) | 24 Gbps (Échantillonnage) | ||

| Densité de puce | 2 Go (16 Gb) | 2 Go (16 Gb) | 2 Go (16 Gb) | ||

| B/W Total (bus 256 bits) | 1024 Go/s | 768 Go/s | 768 Go/s | ||

| Tension DRAM | 1,2 V | 1,35 V | 1,35 V | ||

| Taux de données | QDR | QDR | QDR | ||

| Signalisation | PAM-3 | PAM-4 | NRZ (binaire) | ||

| Densité maximale | 64 Gb | 32 Gb | 32 Gb | ||

| Conditionnement | 266 FBGA | 180 FBGA | 180 FBGA | ||

La première génération de GDDR7 devrait fonctionner à des débits de données d’environ 32 Gbps par broche, et les constructeurs de mémoire ont déjà parlé de débits allant jusqu’à 36 Gbps/broche qui sont facilement réalisables. Cependant, la norme GDDR7 elle-même laisse de la place pour des débits de données encore plus élevés, allant jusqu’à 48 Gbps/broche. JEDEC a même vanté des puces mémoire GDDR7 atteignant « jusqu’à 192 Go/s [32b @ 48 Gbps] par dispositif » dans leur communiqué de presse. Notamment, il s’agit d’une augmentation significativement plus élevée de la bande passante que ce que la signalisation PAM3 apporte seule, ce qui indique qu’il y a plusieurs niveaux d’améliorations dans la conception du GDDR7.

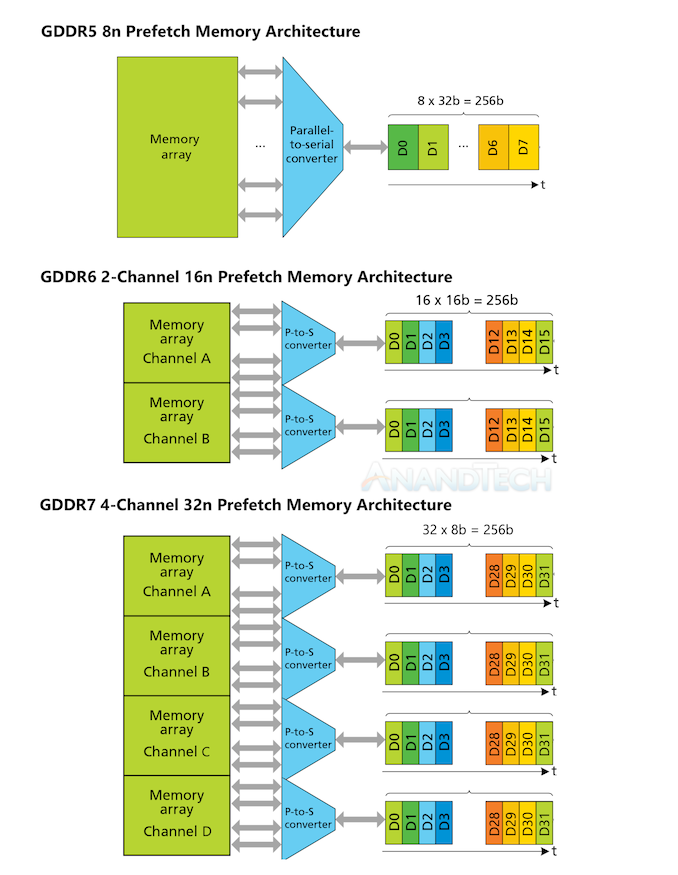

En examinant plus en détail les caractéristiques, JEDEC a à nouveau subdivisé une seule puce mémoire GDDR de 32 bits en un plus grand nombre de canaux. Alors que le GDDR6 offrait deux canaux de 16 bits, le GDDR7 élargit cela à quatre canaux de 8 bits. Cette distinction est quelque peu arbitraire du point de vue de l’utilisateur final – il s’agit toujours d’une puce de 32 bits fonctionnant à 32 Gbps/broche, quelle que soit sa configuration – mais elle a un impact considérable sur le fonctionnement interne de la puce. En particulier, JEDEC a conservé la taille d’anticipation de 256 bits par canal du GDDR5 et du GDDR6, ce qui fait du GDDR7 une conception d’anticipation de 32n.

Architecture de canal GDDR. Diagramme original de l’ère GDDR6 avec l’aimable autorisation de Micron

Le résultat net de tout cela est que, en divisant par deux la largeur du canal mais en conservant la taille d’anticipation inchangée, JEDEC a effectivement doublé la quantité de données qui sont anticipées par cycle des cellules DRAM. C’est un truc assez standard pour étendre la largeur de bande de la mémoire DRAM et c’est essentiellement la même chose que ce que JEDEC a fait avec le GDDR6 en 2018. Cela rappelle simplement que les cellules DRAM sont toujours très lentes (de l’ordre de plusieurs centaines de MHz) et ne deviennent pas plus rapides. Donc, la seule façon de nourrir des bus mémoire plus rapides est de récupérer des quantités de données de plus en plus importantes en une seule fois.

Le changement du nombre de canaux par puce mémoire a également un impact mineur sur le fonctionnement du mode « coquillage » multi-canaux pour les configurations de mémoire de capacité supérieure. Alors que le GDDR6 accédait à un seul canal de mémoire à partir de chaque puce dans une configuration de coquillage, le GDDR7 accédera à deux canaux – ce que JEDEC appelle le mode à deux canaux. Plus précisément, ce mode lit les canaux A et C de chaque puce. Il est effectivement identique au comportement du mode coquillage avec le GDDR6, ce qui indique que, bien que les configurations de coquillage restent prises en charge dans cette dernière génération de mémoire, aucune autre astuce n’est utilisée pour améliorer la capacité de mémoire au-delà des densités de puce de mémoire de plus en plus importantes.

Sur ce point, la norme GDDR7 ajoute officiellement le prise en chage de dispositifs DRAM de 64 Gbit, soit le double de la capacité maximale de 32 Gbit du GDDR6/GDDR6X. Les capacités non puissances de deux continuent également d’être prises en charge, permettant des puces de 24 Gbit et 48 Gbit. Le prise en chage de puces mémoire de plus grande capacité pousse encore plus la capacité mémoire maximale d’une carte vidéo haut de gamme théorique avec un bus mémoire de 384 bits à aussi haut que 192 Go de mémoire – un développement qui serait sans aucun doute bien accueilli par les opérateurs de centres de données à l’ère des gros modèles d’IA avec des langages. Cela évoqué, nous continuons régulièrement à voir des puces mémoire de 16 Gbit utilisées sur les cartes mémoire actuelles, même si le GDDR6 prend en charge des puces de 32 Gbit. Couplé au fait que Samsung et Micron ont déjà révélé que leur première génération de puces GDDR7 atteindra également respectivement 16 Gbit/24 Gbit au maximum, on peut dire en toute sécurité que les puces de 64 Gbit sont encore assez loin dans le futur (donc ne vendez pas encore vos cartes 48 Go).

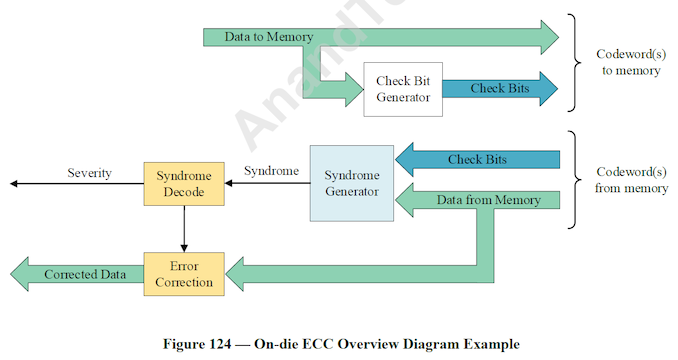

Pour leur dernière génération de technologie mémoire, JEDEC inclut également plusieurs nouvelles fonctionnalités de fiabilité inédites pour GDDR. Plus particulièrement, les capacités ECC intégrées, similaires à ce que nous avons vu avec l’introduction de la DDR5. Et bien que nous n’ayons pas pu obtenir de commentaire officiel de JEDEC sur la raison pour laquelle ils ont choisi d’inclure maintenant le prise en chage de l’ECC, son inclusion n’est pas surprenante compte tenu des exigences en matière de fiabilité pour la DDR5. En bref, à mesure que les densités des puces mémoire ont augmenté, il est devenu de plus en plus difficile d’obtenir une matrice « parfaite » sans défauts; ainsi, l’ajout de l’ECC intégré permet aux constructeurs de mémoire de maintenir le fonctionnement fiable de leurs puces face à des erreurs inévitables.

Cette figure est reproduite, avec autorisation, à partir du document JEDEC JESD239, figure 124

En interne, la caractéristique GDDR7 exige un minimum de 16 bits de données de parité pour 256 bits de données utilisateur (6,25%), JEDEC donnant un exemple de mise en œuvre d’un code de correction d’erreur à un seul bit de 9 bits (SEC) plus un contrôle de redondance cyclique de 7 bits (CRC). Dans l’ensemble, l’ECC intégré à la GDDR7 devrait être capable de corriger 100 % des erreurs d’un bit et de détecter 100 % des erreurs de deux bits, tombant à 99,3 % dans le cas rare des erreurs de trois bits. Les informations sur les erreurs de mémoire sont également mises à la disposition du contrôleur de mémoire, via ce que JEDEC appelle son protocole de transparence de l’ECC intégré. Et bien que techniquement distinct de l’ECC lui-même, le GDDR7 jette également un autre élément de fiabilité de la mémoire avec une parité d’adresses de commande avec un blocage de commande (CAPARBLK), qui est destiné à améliorer l’intégrité du bus d’adresses de commande.

Sinon, bien que l’inclusion de l’ECC intégré ne devrait pas avoir plus d’impact sur les cartes vidéo grand public que son inclusion ne l’a eu pour la mémoire DDR5 et les plateformes grand public, il reste à voir ce que cela signifiera pour les cartes vidéo de postes de travail et de serveur. Les constructeurs là-bas utilisent depuis plusieurs générations déjà une ECC logicielle sur une mémoire non protégée ; il est donc probable que cela restera le cas pour les cartes GDDR7, mais l’utilisation régulière de l’ECC logicielle rend les choses beaucoup plus flexibles que dans l’espace des CPU.

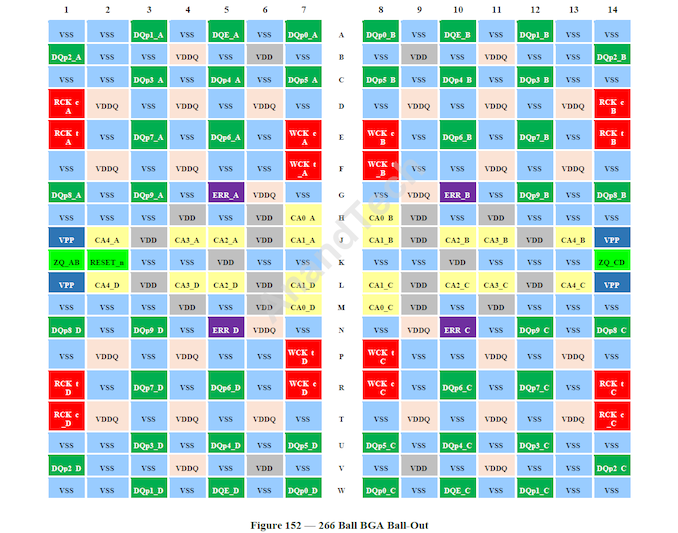

Cette figure est reproduite, avec autorisation, à partir du document JEDEC JESD239, figure 152

Enfin, le GDDR7 introduit également une série d’autres fonctionnalités liées à la fiabilité, principalement liées à l’aide à l’opération PAM3. Cela comprend des motifs d’entraînement LFSR (registre à décalage à rétroaction linéaire) indépendants du cœur avec masque d’œil et compteurs d’erreurs. Les motifs d’entraînement LFSR sont utilisés pour tester et ajuster l’interface (afin d’assurer l’efficacité), le masquage de l’œil évalue la qualité du signal, et les compteurs d’erreurs suivent le nombre d’erreurs pendant l’entraînement.

Outre les questions techniques, l’annonce de cette semaine inclus des déclarations de support de tous les acteurs habituels des deux côtés de l’échiquier, y compris AMD et NVIDIA, ainsi que le trio Micron/Samsung/SKhynix. Il va sans dire que toutes les parties sont impatientes d’utiliser ou de vendre respectivement la GDDR7, étant donné les améliorations de capacité de mémoire et de bande passante qu’elle apportera – et surtout à une époque où tout ce qui est destiné au marché de l’IA se vend comme des petits pains.

Aucun produit spécifique n’est annoncé pour le moment, mais avec Samsung et Micron ayant déjà annoncé leur intention de lancer la mémoire GDDR7 cette année, nous devrions voir de nouvelles mémoires (et de nouveaux GPU pour les accompagner) plus tard cette année.

Les normes et publications JEDEC sont protégées par des droits d’auteur de la JEDEC Solid State Technology Association. Tous droits réservés.