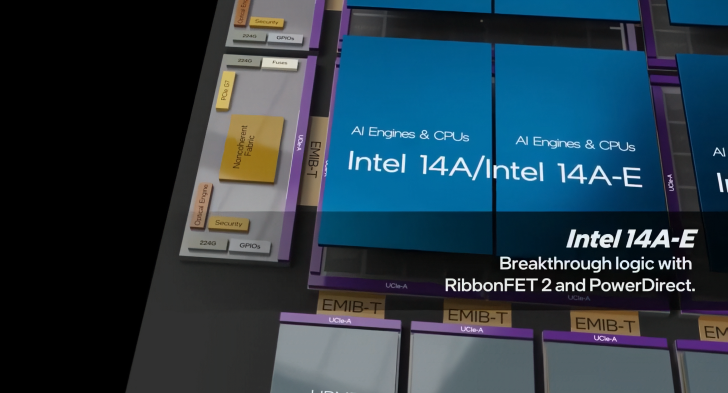

Intel présente ses capacités de packaging avancées : plus de 12X réticule avec 16 tiles sur nœuds 18A/14A et jusqu’à 24 sites HBM

Intel a récemment mis en avant ses solutions d’emballage avancées avec un produit multi-chiplet intégrant les technologies des nœuds 18A et 14A, ainsi que Foveros 3D et EMIB-T.

Technologies Intel 18A/14A : jusqu’à 16 unités de calcul et 24 sites HBM

Intel ne fait pas de compromis sur ses solutions d’emballage et a présenté des modèles qui dessinent l’avenir des puces axées sur les jeux, l’IA et les centres de données. Ces technologies devraient rivaliser avec les solutions CoWoS de TSMC, qui exploitent le nœud A16 et plusieurs sites HBM4E.

Les innovations d’Intel incluent le Intel 14A-E avec son RibbonFET 2 pour un rendement inédit, et le Intel 18A-PT qui améliore la densité et la fiabilité énergétique. L’architecture est conçue pour dépasser les limites traditionnelles, utilisant le Foveros Direct 3D pour empiler les composants avec précision et EMIB-T pour une bande passante plus élevée.

Conception et connectivité des puces

Un des modèles présentés comporte quatre unités de calcul et 12 sites HBM, tandis qu’un autre en comprend 16 avec 24 sites HBM. Ce design pourrait potentiellement héberger jusqu’à 48 contrôleurs LPDDR5X, augmentant la densité pour les applications d’IA et de centres de données.

Le chip présente un die de base utilisant le processus 18A-PT, intégrant le SRAM. La technologie de base s’inspire de Clearwater Forest, qui exploite 576 Mo de cache L3 sur ses solutions. Le die de calcul principal est relié à la base par l’architecture Foveros 3D, facilitant les interconnexions.

Ce modèle innovant souligne l’engagement d’Intel vers un écosystème robuste, visant à répondre rapidement aux attentes des partenaires industriels pour renforcer leur chaîne d’approvisionnement. Alors qu’Intel a dominé l’emballage avancé, la concrétisation de ces projets sera décisive pour l’avenir de l’entreprise.