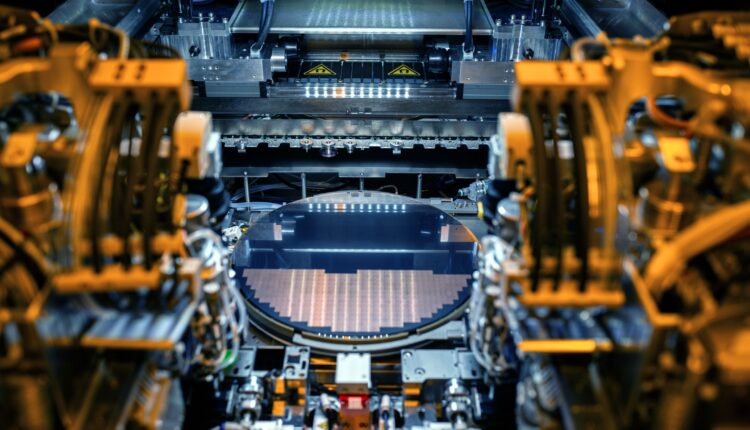

Intel Foundry a récemment révélé des avancées significatives dans le domaine des technologies de transistors et d’emballage, mettant l’accent sur l’innovation en matière de matériaux et de silicium.

Nouvelles Innovations : Ruthénium Subtractif et Technologies de Transistors

Lors de la réunion internationale sur les dispositifs électroniques (IEDM) en 2024, Intel Foundry a annoncé des percées destinées à propulser l’industrie des semi-conducteurs vers la prochaine décennie. Parmi ces innovations, l’utilisation du ruthénium subtractif permet une amélioration de l’interconnexion au sein des puces, avec une réduction de 25% de la capacité.

Intel Foundry a également présenté une amélioration de 100x de productivité grâce à une solution d’intégration hétérogène pour un emballage avancé, assurant une assemblée rapide des puces. Cette initiative vise à optimiser le scaling des transistors en démontrant l’utilisation de la technologie RibbonFET CMOS et des modules d’oxyde de grille pour des dispositifs performants.

Importance des avancées : À l’approche de l’objectif d’un billion de transistors par puce d’ici 2030, les progrès en matière de recouvrement de transistors et de mise à l’échelle des interconnexions sont cruciaux pour répondre à la demande croissante en applications informatiques écoénergétiques, performantes et économiques, notamment dans le domaine de l’IA.

Technologies de Matériaux et Avantages Concurrentiels

Pour maintenir un rythme de développement, Intel Foundry a commencé à explorer de nouveaux matériaux qui soutiennent des solutions comme PowerVia, facilitant ainsi la gestion de l’interconnexion. Ces stratégies sont essentielles pour la continuité des principes de Moore et l’évolution des semi-conducteurs vers des applications avancées en IA.

Intel Foundry a proposé plusieurs approches innovantes pour surmonter les limitations des transistors en cuivre dans la mise à l’échelle des interconnexions. Cela inclut des techniques d’assemblage améliorées et des feuilles de route définies pour le scaling des transistors :

- Ruthénium Subtractif : Présenté comme une alternative clé, il permet une réduction significative de la capacité grâce à l’intégration d’airgaps, sans exiger des zones d’exclusion lithographique coûteuses, favorisant une fabrication de haute volumé.

- Transfert de Couche Sélectif : Cette méthode offre jusqu’à 100x de productivité pour l’assemblage de puces ultra-rapides, permettant des tailles de puce plus petites et une plus grande flexibilité.

- Silicon RibbonFET CMOS : Intel Foundry a démontré des transistors CMOS à une longueur de grille de 6 nm, intégrant des effets de court-circuit de premier ordre pour un meilleur rendement.

- Oxyde de Grille pour FETs 2D GAA : En se concentrant sur la fabrication de dispositifs avec une longueur de grille réduite à 30 nm, la recherche sur les semiconducteurs à dichalcogénures de transition pourrait signifier une avancée majeure.

De plus, Intel Foundry a progressé dans la recherche sur la technologie de nitrure de gallium (GaN) de 300 mm, qui se distingue par ses performances élevées en électronique de puissance et radio-fréquence, capable de supporter des voltages et des températures plus élevés.

Vision Future et Appels à l’Action

Lors de la conférence IEDM, la vision d’Intel Foundry pour l’avenir du packaging avancé et du scaling des transistors a été esquissée. Trois axes clés d’innovation ont été identifiés :

- Intégration de mémoire avancée pour résoudre les bottleneck (goulots d’étranglement) en capacité et en bande passante.

- Bondage hybride pour l’optimisation de la bande passante d’interconnexion.

- Expansion de systèmes modulaires avec des solutions de connectivité associées.

Enfin, Intel Foundry a lancé un appel pour développer des innovations tests nécessaires à une mise à l’échelle continue des transistors à l’aube de l’ère du billion de transistors. Le développement de transistors fonctionnant à ultra-basse tension (moins de 300 millivolts) vise à résoudre des problèmes thermiques croissants et à améliorer de manière significative la consommation d’énergie.