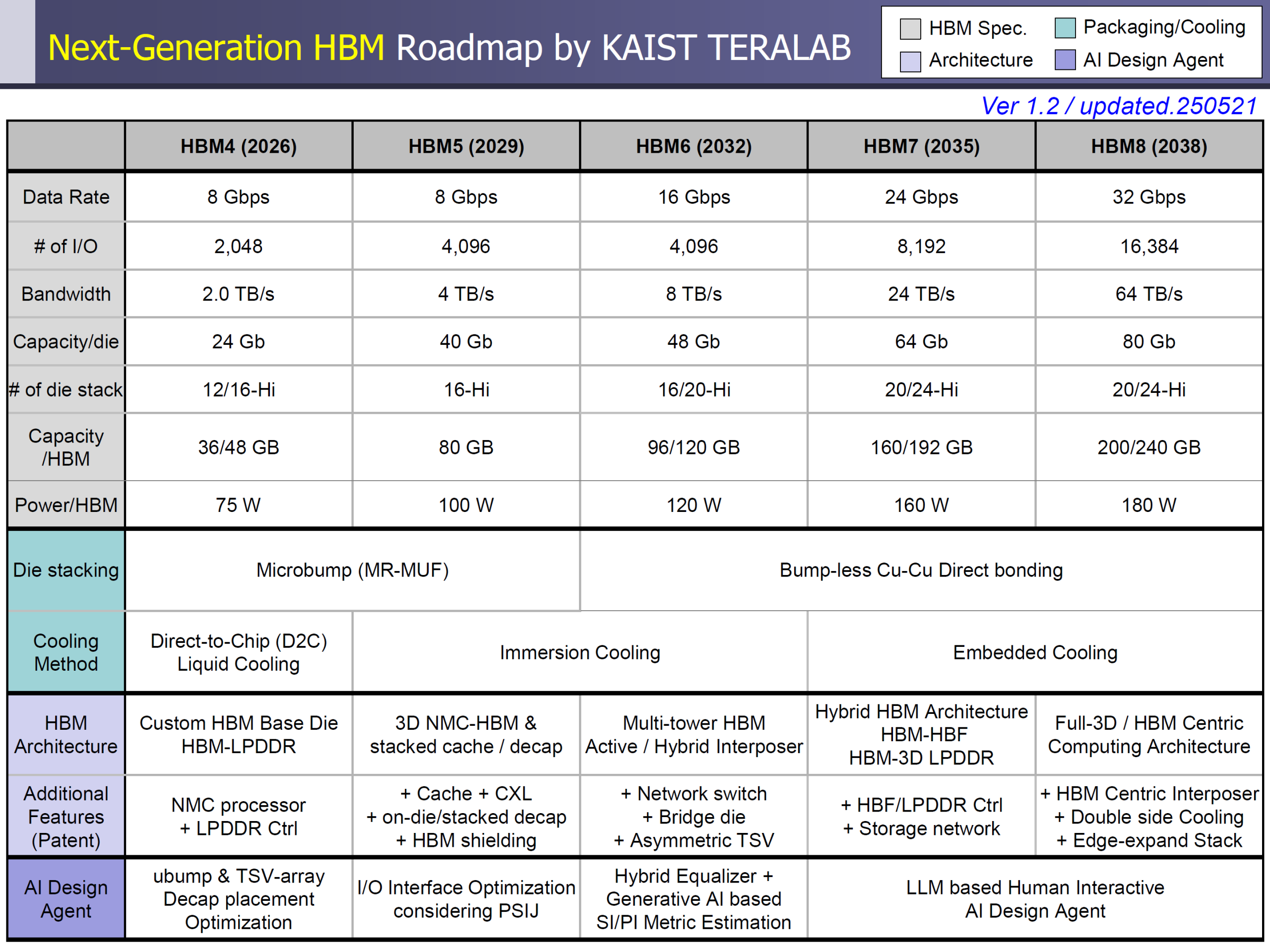

Évolution des standards HBM : HBM4 à HBM8 pour répondre aux besoins des centres de données et de l’IA

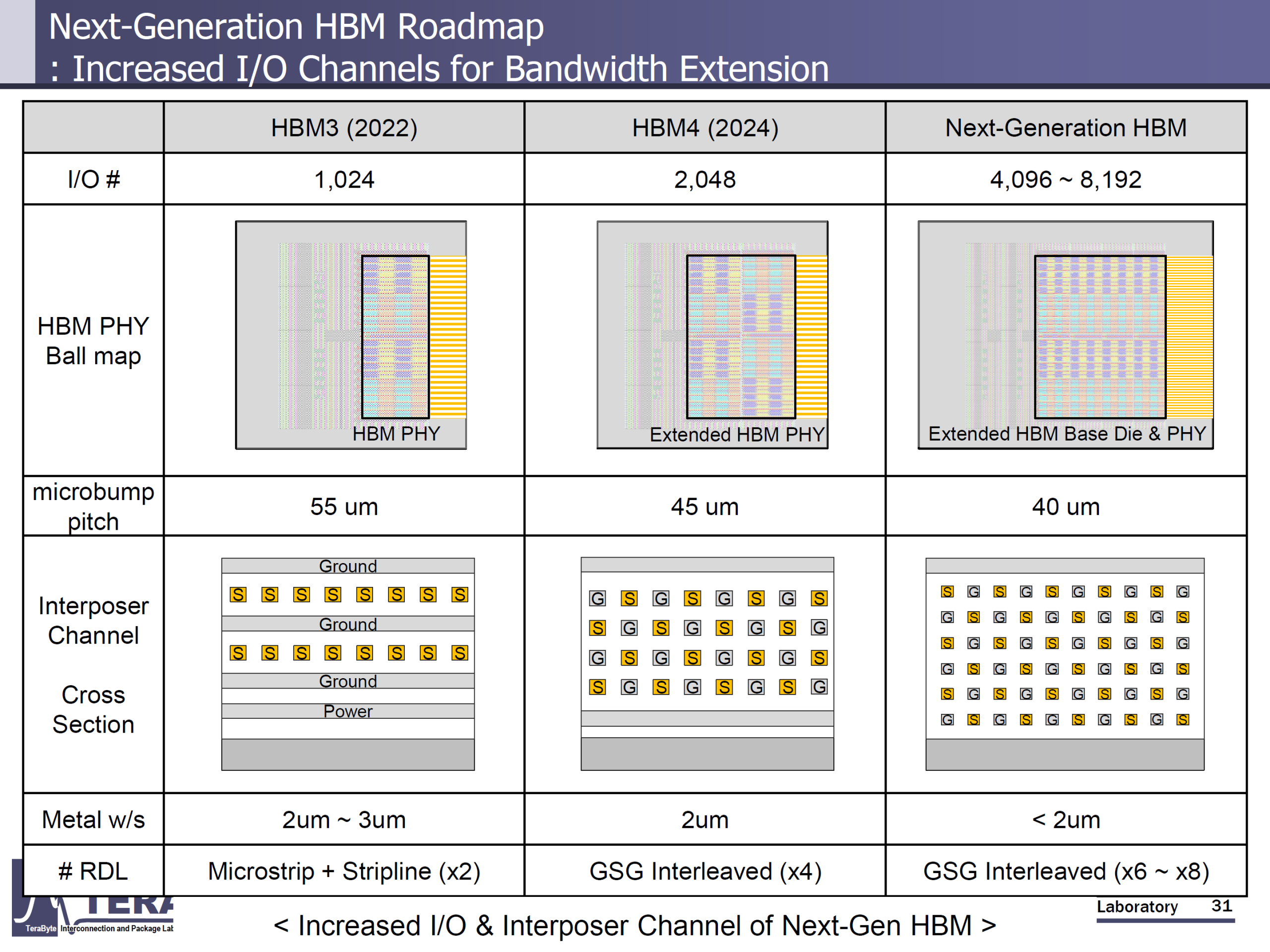

Les évolutions des standards HBM de nouvelle génération, incluant HBM4, HBM5, HBM6, HBM7 et HBM8, promettent d’importantes avancées pour répondre aux besoins croissants des centres de données et de l’intelligence artificielle.

Une Évolution de la Mémoire HBM Contre la Demande Croissante de l’IA

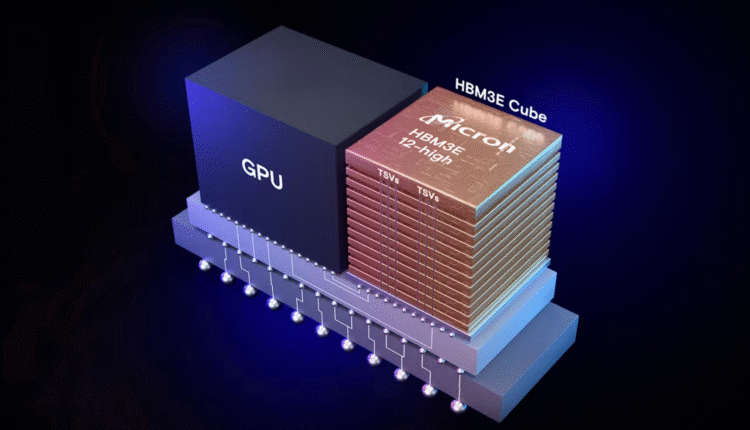

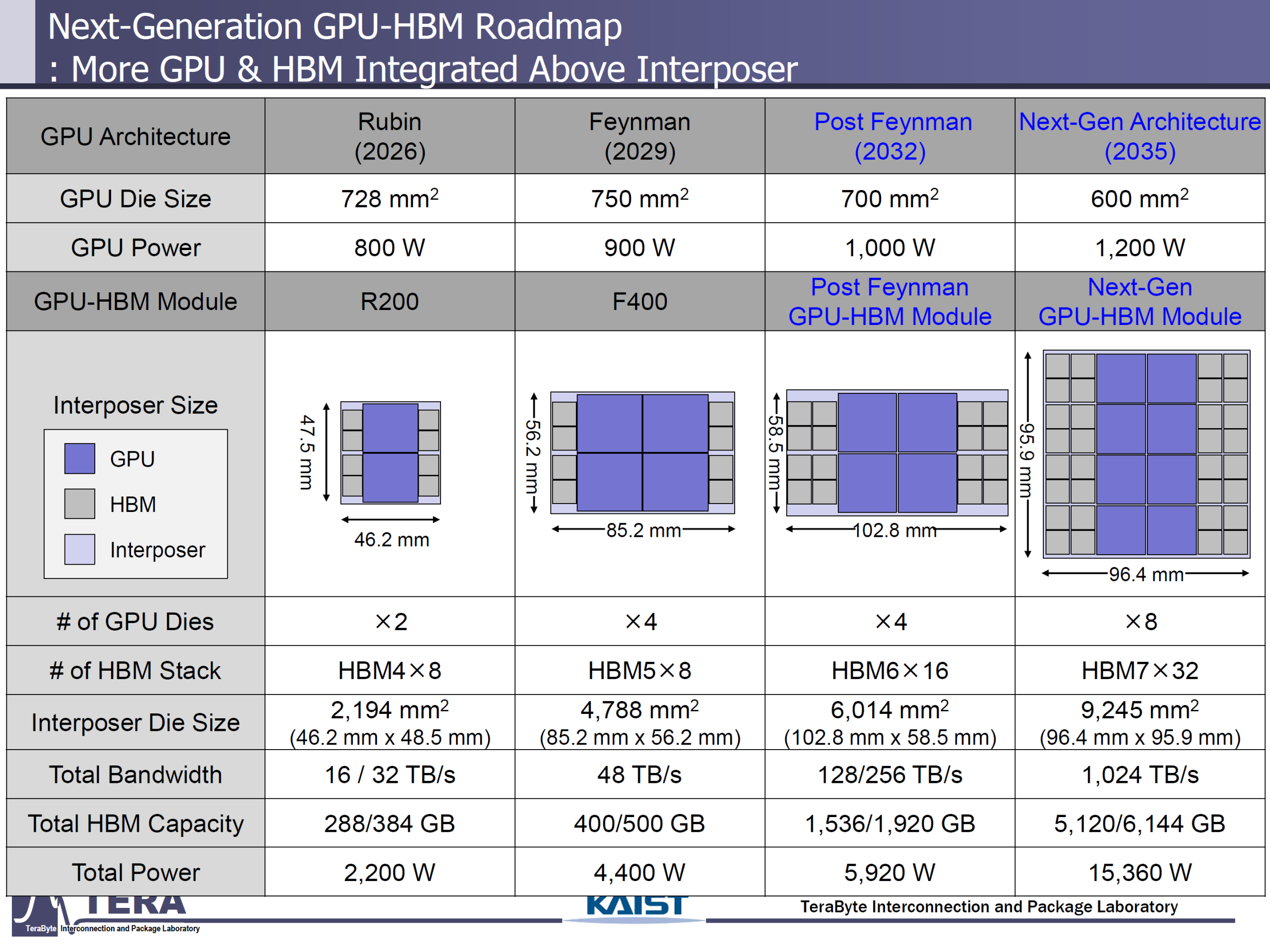

Lors d’une récente présentation, le KAIST et Tera (Laboratoire d’interconnexion et d’emballage de téraoctets) ont esquissé la roadmap pour les HBM. Plusieurs nouveaux standards HBM sont prévus, tels que HBM4 à HBM8, chacun apportant son lot d’innovations à analyser en profondeur.

Commençons par HBM4, qui devrait devenir le standard incontournable pour les centres de données de prochaine génération et les GPU d’IA lancés en 2026. AMD et NVIDIA ont déjà confirmé son utilisation pour leurs gammes MI400 et Rubin.

Des informations concernant la roadmap de NVIDIA ont également été fournies. TeraByte, spécialisé dans les méthodes d’interconnexion et d’emballage pour la mémoire HBM, suggère que ces détails sont significatifs.

HBM4 Pour les GPUs Rubin de NVIDIA et MI500 d’AMD

Le modèle Rubin de NVIDIA et sa version Ultra utiliseront respectivement HBM4 et HBM4e. Dans la roadmap officielle, Rubin comprend huit sites HBM4, tandis que Rubin Ultra en comporte seize. L’Ultra affiche une densité de calcul supérieure grâce à une section transversale de GPU plus large.

Selon les études, la taille du die du GPU Rubin sera de 728 mm², consommant 800 W par die. L’interposeur mesurera 2194 mm² et soutiendra entre 288 à 384 Go de VRAM avec une bande passante de 16 à 32 To/s.

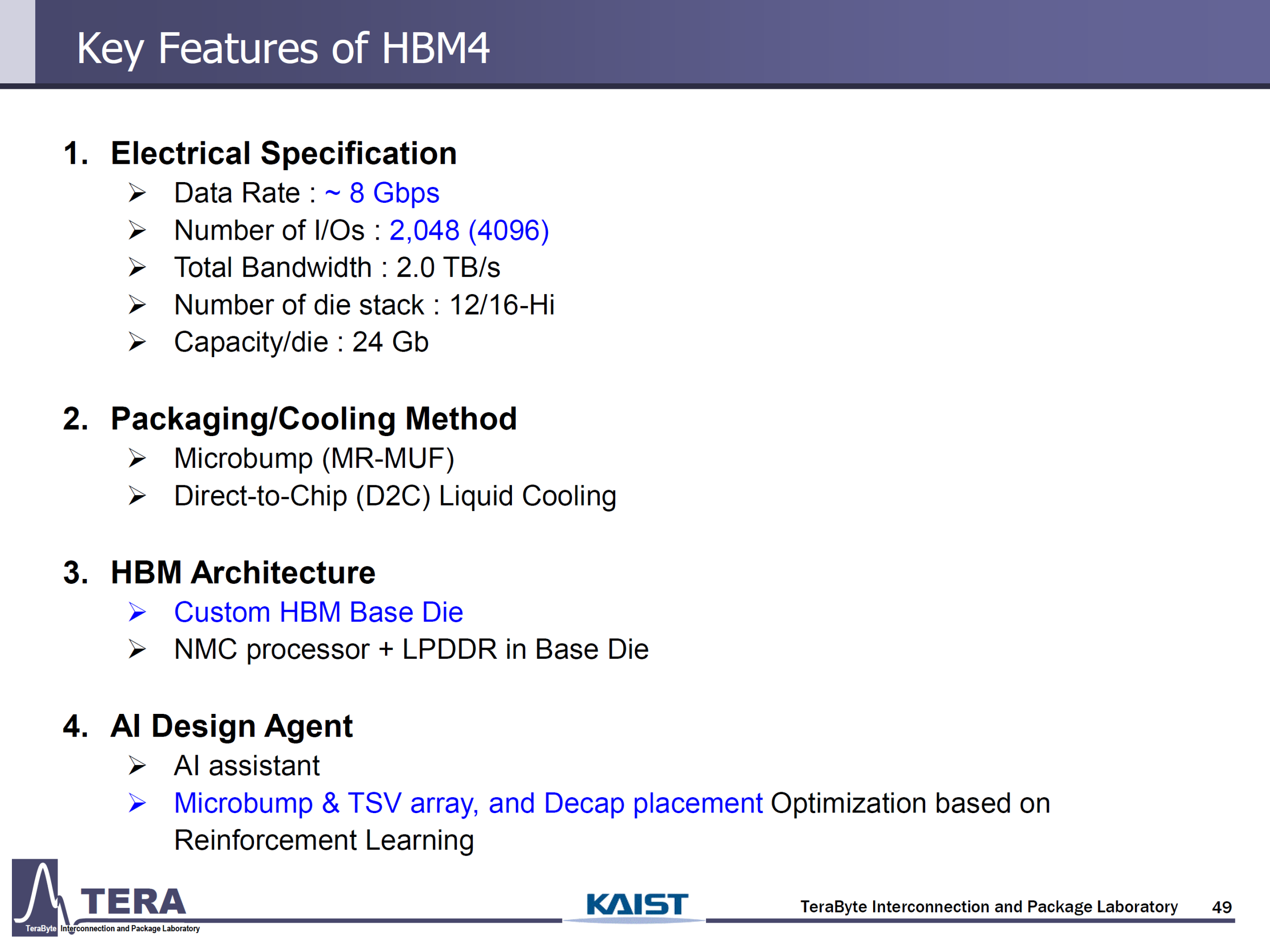

Les principales caractéristiques de la mémoire HBM4 incluent :

- Taux de données : ~ 8 Gbps

- Nombre d’I/Os : 2048 (4096)

- Bande passante totale : 2.0 To/s

- Nombre de piles de die : 12/16-Hi

- Capacité par die : 24 Gb

- Capacité par HBM : 36/48 Go

- Puissance par HBM : 75 W

- Méthode d’emballage : Microbump (MR-MUF)

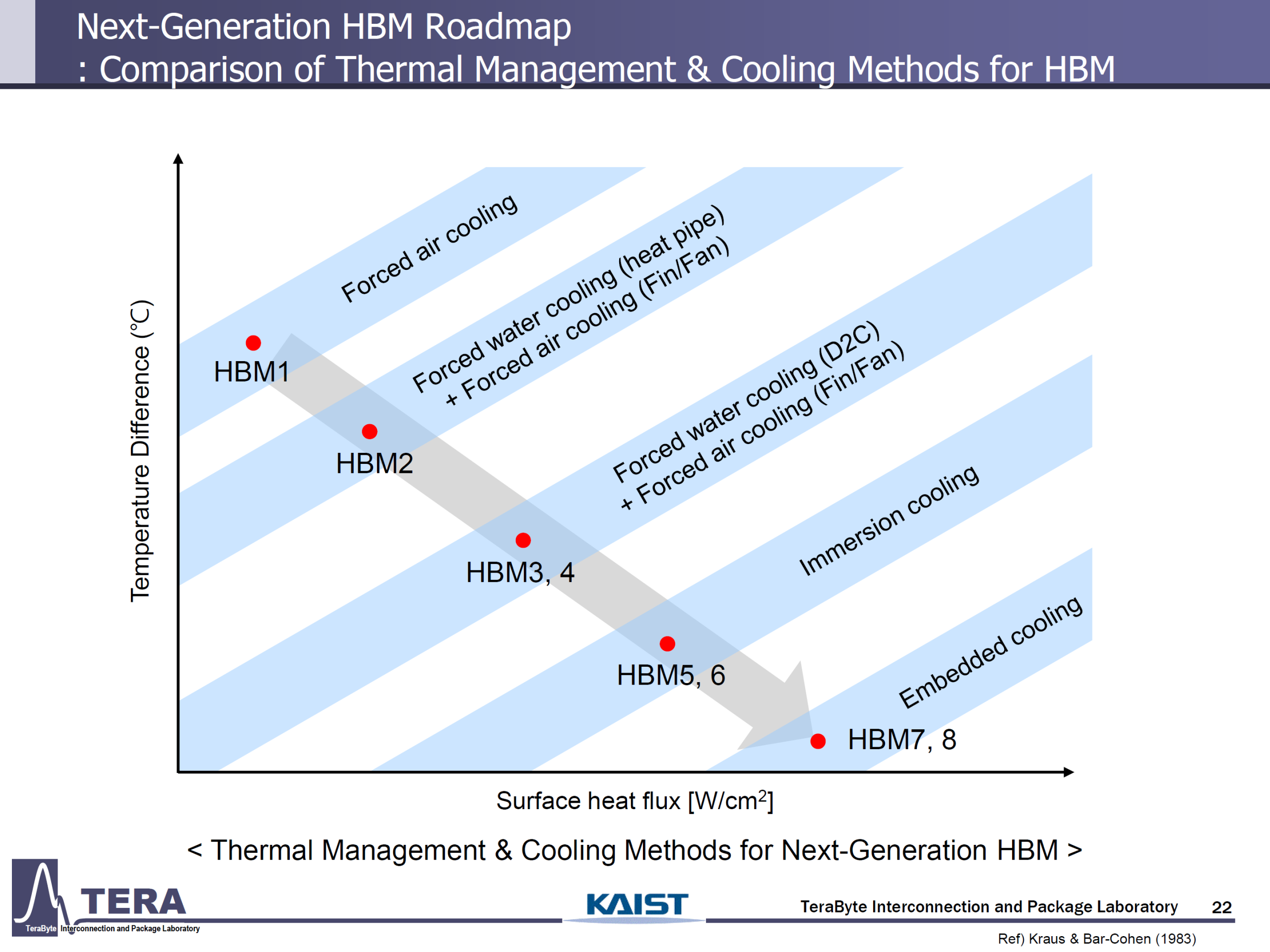

- Méthode de refroidissement : Refroidissement liquide direct au chip (D2C)

De manière intéressante, l’Instinct MI400 d’AMD augmentera la capacité de HBM4 à 432 Go, atteignant une bande passante de mémoire allant jusqu’à 19.6 To/s.

Les caractéristiques de HBM4 visent un taux de données de 8 Gbps, avec un I/O de 2048 bits, et une bande passante de mémoire de 2.0 To/s par pile, en visant une capacité maximale de 36 à 48 Go.

La version HBM4e promet d’atteindre un taux de 10 Gbps avec 2.5 To/s de bande passante, et une capacité par die plafonnée à 32 Gb.

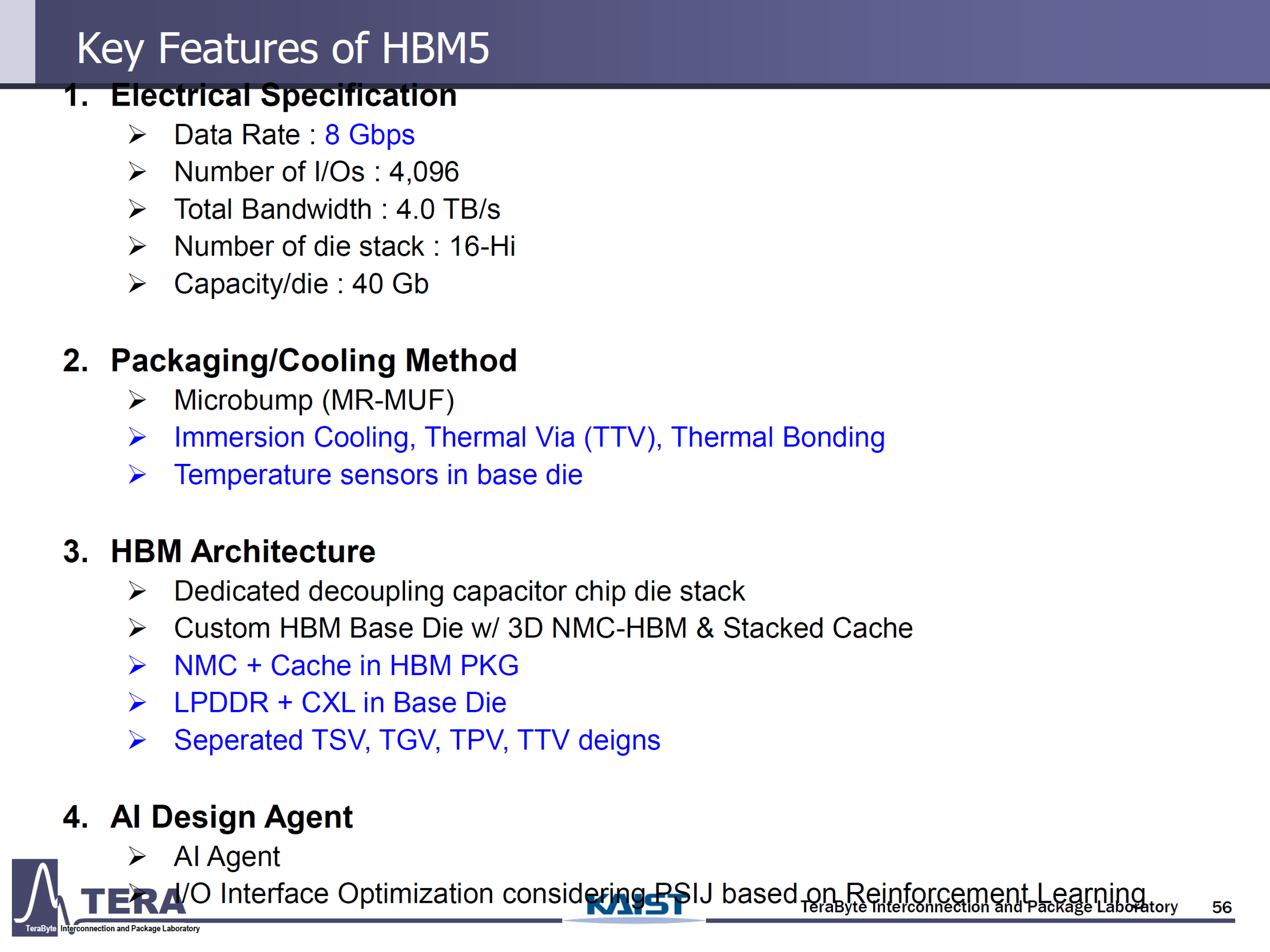

HBM5 Vise NVIDIA Feynman avec une Lancement Prévus Pour 2029

Pour HBM5, le taux de données devrait demeurer à 8 Gbps pour l’option non-e, mais avec plus d’I/O, atteignant 4096 bits. La bande passante augmentera à 4 To/s et le standard visera des capacités allant jusqu’à 80 Go par pile.

Caractéristiques principales de la norme de mémoire HBM5 :

- Taux de données : 8 Gbps

- Nombre d’I/Os : 4096

- Bande passante totale : 4.0 To/s

- Nombre de piles de die : 16-Hi

- Capacité par die : 40 Gb

- Capacité par HBM : 80 Go

- Puissance par HBM : 100 W

- Méthode d’emballage : Microbump (MR-MUF)

- Méthode de refroidissement : Refroidissement par immersion et autres techniques

NVIDIA Feynman devrait être le premier GPU à utiliser le standard HBM5, avec un lancement projeté pour 2029.

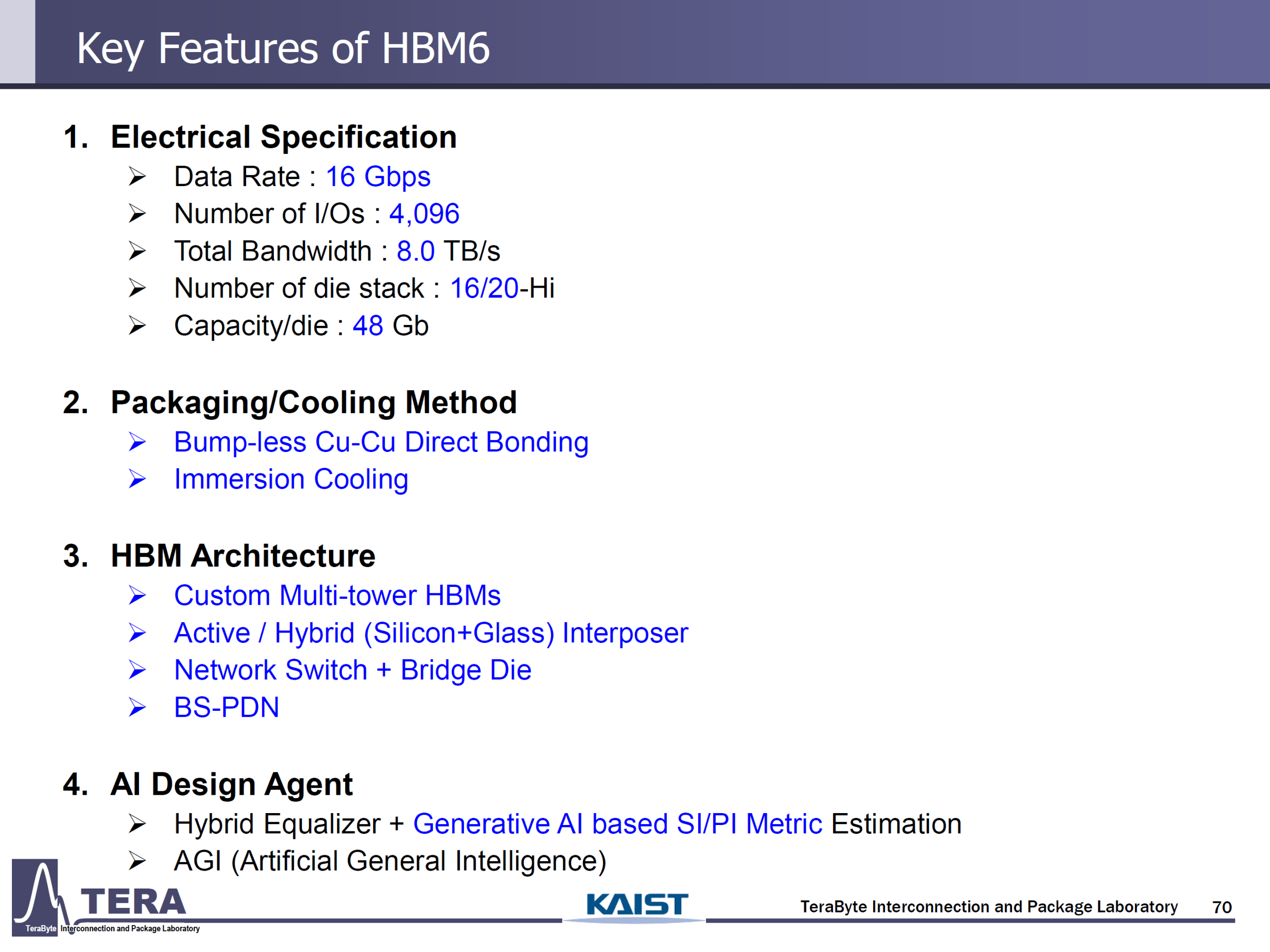

HBM6 Pour l’Architecture Post-Feynman – Capacités Massives et Bande Passante Élevée

L’architecture HBM6 prévoit un taux de données doublé à 16 Gbps, et les lanes I/O passant à 4096, le tout visant 8 To/s de bande passante.

Les caractéristiques de la norme de mémoire HBM6 incluent :

- Taux de données : 16 Gbps

- Nombre d’I/Os : 4096

- Bande passante totale : 8.0 To/s

- Nombre de piles de die : 16/20-Hi

- Capacité par die : 48 Gb

- Capacité par HBM : 96/120 Go

- Puissance par HBM : 120 W

- Méthode d’emballage : Bump-less Cu-Cu Direct Bonding

- Méthode de refroidissement : Refroidissement par immersion

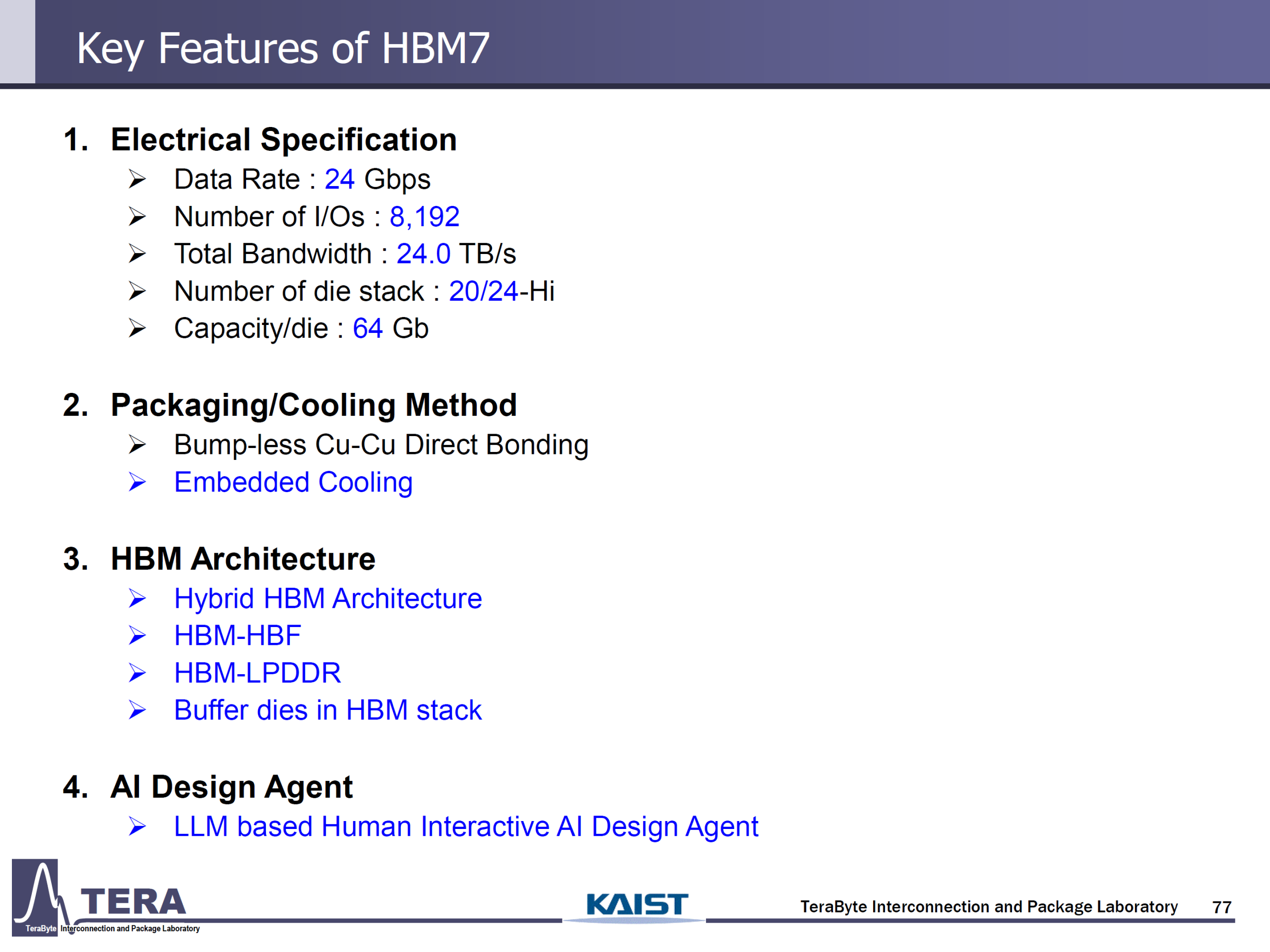

HBM7 et HBM8 vont prolonger cette tendance en augmentant nettement les capacités et la bande passante. HBM7 promet un taux de 24 Gbps. Avec la possibilité d’atteindre jusqu’à 160 Go par pile, la mémoire HBM7 devrait révolutionner le secteur.

HBM8, prévu pour 2038, atteindra un débit de 32 Gbps et une bande passante de 64 To/s, consolidant ainsi l’architecture HBM avec des solutions de refroidissement avancées.

Une Architecture HBF pour des Applications LLM Intensives

Enfin, l’architecture HBF (High-Bandwidth Flash) répond à la demande croissante d’inférences LLM. Elle utilise la NAND superposée pour augmenter la capacité dans un empilement 16-Hi avec interconnexion HBF, permettant ainsi des communications rapides entre les composants.

Cette évolution de l’architecture mémoire pourrait transformer la manière dont les GPUs interagissent avec les mémoires, offrant ainsi une puissance de traitement sans précédent dans les années à venir.