AMD envisage de déplacer une partie de sa production de puces haute performance vers l’usine de TSMC en Arizona d’ici l’année prochaine. Cette décision représente un tournant pour le constructeur de semi-conducteurs, qui a traditionnellement dépendu des installations de TSMC à Taïwan.

Un nouveau chapitre pour la production de puces AMD

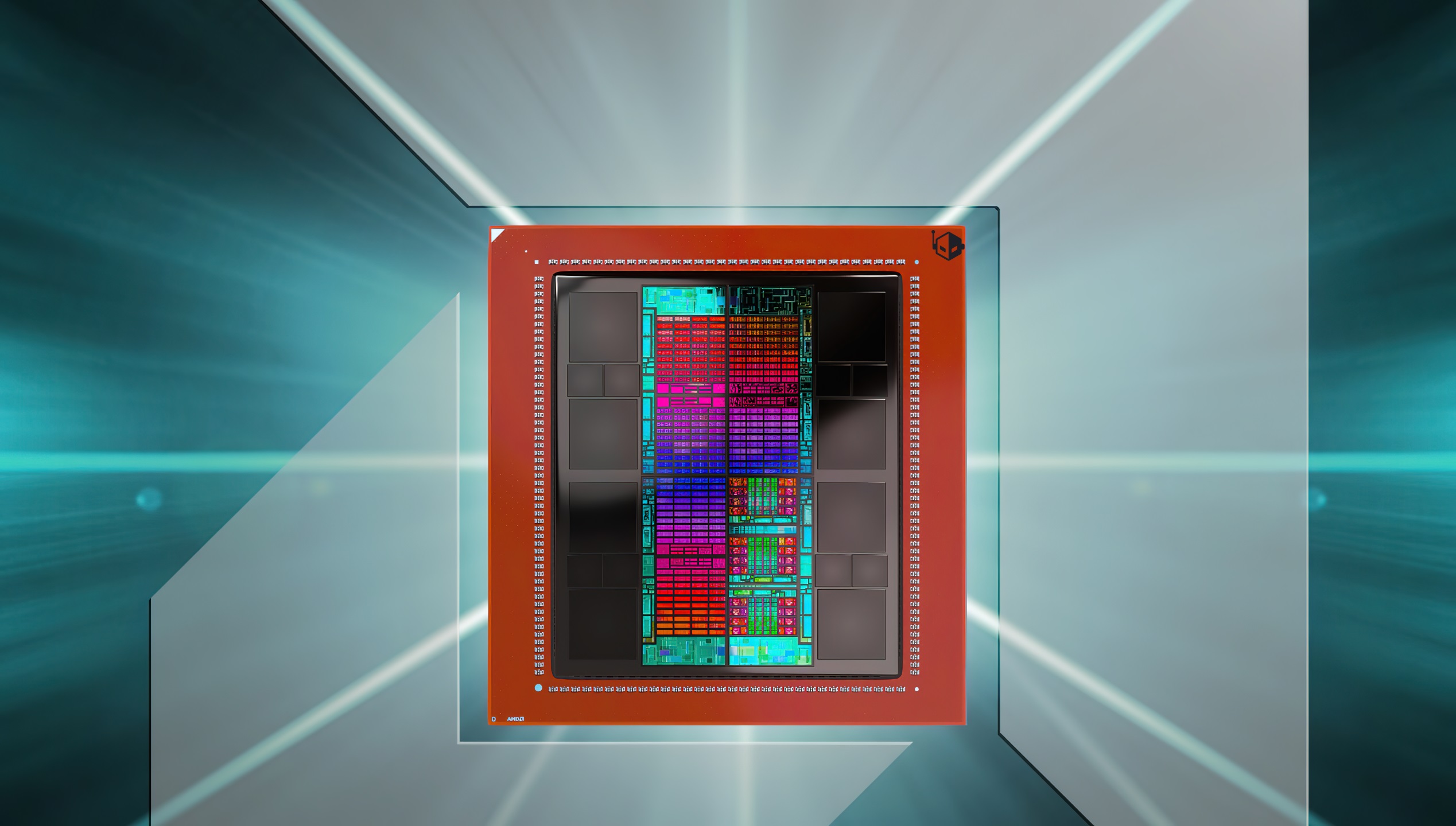

Habituellement, les puces d’AMD, telles que celles de la série Radeon RX 7000 et les dernières gammes Zen 4 et Zen 5, sont fabriquées en utilisant les nœuds de processus de TSMC à Taïwan. Toutefois, il semble que AMD s’oriente vers une fabrication locale en Amérique, ce qui pourrait renforcer la capacité de production nationale.

La construction de l’usine de TSMC en Arizona a débuté en 2021. Bien que l’usine ne compte pas encore de nombreux clients, AMD pourrait devenir l’un des premiers à en bénéficier. Selon des sources, la production des puces haute performance d’AMD est attendue pour 2025.

Les nouvelles puces utiliseront le nœud de 5nm, notamment la version N4. Ce nœud de processus est disponible sous différentes déclinaisons, y compris N5, N5P, N4, N4P, et N4X. La production en volume du N4 a démarré en 2022 et ces puces pourraient être au cœur des nouveaux projets d’AMD.

Peu d’informations ont dévoilé concernant ce programme, car les responsables ont décliné tout commentaire sur les clients ou les produits de TSMC. Néanmoins, il est évident que les États-Unis tendent vers une chaîne d’approvisionnement complète en hardware d’IA, avec des initiatives telles que la fabrication de l’Apple A16 à l’usine de TSMC en Arizona.

Récemment, Amkor a annoncé une collaboration avec TSMC pour l’emballage avancé en Arizona. Les deux entreprises travaillent sur des technologies d’emballage de pointe, notamment l’Integrated Fan-Out et le Chip Wafer on Substrate.

La technologie d’emballage par niveau de wafer InFO permet une disposition plus rapprochée des puces, offrant ainsi un coût réduit pour la fabrication. En revanche, le CoWoS est plus efficace pour relier la mémoire à large bande passante aux cœurs GPU, mais il est également plus coûteux. Ce dernier sera essentiel pour les puces haute performance d’AMD et de NVIDIA, tandis qu’Apple pourrait s’en sortir avec InFO pour ses appareils mobiles.