AMD passe des SERDES à un interconnect D2D « Sea-of-Wires » pour les futurs CPU Zen 6 avec gains d’efficacité et de latence

AMD se prépare à un grand bond en avant avec la technologie de connexion D2D sur ses processeurs Zen 6. Un aperçu intéressant a déjà été fourni grâce aux APUs Strix Halo.

Améliorations de puissance et de latence avec Strix Halo

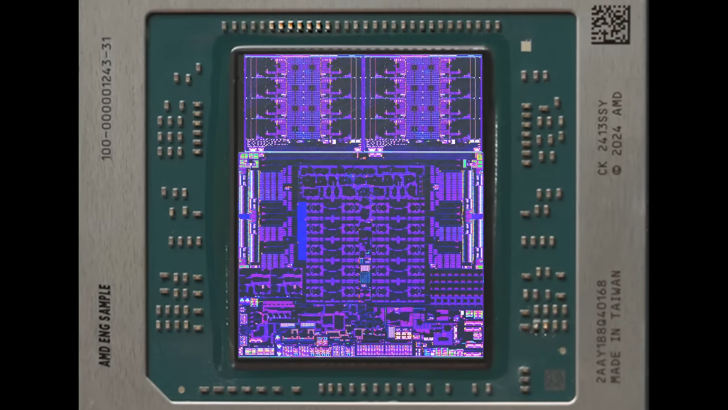

Avant d’entrer dans les détails, il est important de saluer le travail de High Yield qui a mis en lumière le changement dans la connectivité D2D avec les Strix Halo. AMD, en intégrant des avancées de processus et des designs repensés, vise à maximiser les performances. Malgré l’utilisation d’une technologie similaire depuis Zen 2 pour les interconnexions D2D, les processeurs Zen 6 pourraient introduire de nouvelles méthodes. Certains éléments de ‘Zen 6 DNA‘ se retrouvent déjà dans les APUs Strix Halo.

Pour établir une communication entre les dies, AMD utilise des ‘SERDES PHYs’ sur les bords des dies CCD. Cette technologie permet des communications à haute vitesse via le substrat organique. La conversion de données parallèles en flux série facilite la liaison entre les CCD. Toutefois, cette méthode présente des inconvénients notables, notamment en termes de latence et de consommation d’énergie due à la sérialisation.

La Nouvelle Méthode de Connectivité et ses Avantages

Avec Strix Halo, AMD adopte une méthode révolutionnaire grâce à la technologie InFO-oS de TSMC associée à un plan de redistribution (RDL). Ce nouveau système établit des connexions parallèles courtes entre les dies, permettant une communication efficace et rapide. Cette restructuration réduit les besoins en latence et en consommation d’énergie, tout en augmentant la bande passante globale.

Bien que des défis demeurent concernant la complexité de conception liée au RDL multicouche, les avantages apportés par ce système sont significatifs. Quoi qu’il en soit, l’approche adoptée par AMD avec Strix Halo devrait jouer un rôle clé dans les performances des futurs processeurs Zen 6.